En el foro anual de tecnología de 2018, Noel Hurley, vicepresidente de estrategia para el grupo de productos IP de brazo (Grupo IP), dijo que se avecina la "quinta ola", que involucra tres tecnologías clave de Internet of Things, 5G e inteligencia artificial. Nube, red y nuestros dispositivos. Entre ellos, el Internet de las cosas generará una gran cantidad de datos, 5G asume la tarea de transmisión de datos, la inteligencia artificial puede ayudarnos a comprender y procesar estos datos. La convergencia de estas tres tecnologías nos ha traído nuevas oportunidades en el campo de la tecnología. Con este fin, debemos establecer un sistema muy seguro lo antes posible para garantizar la seguridad de los datos. Estas son todas las áreas en las que el brazo está involucrado y continúa invirtiendo.

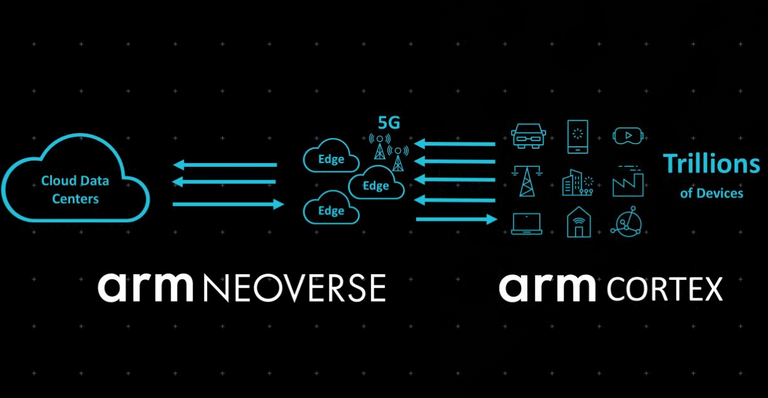

Neoverse: sentar las bases de una infraestructura de nube a borde para billones de dispositivos conectados inteligentes

Los centros de datos modernos ya no son una estructura física, sino un centro de datos e informática en la nube y en el borde. Más que nunca, las empresas deben considerar diseños de centros de datos interconectados e distribuidos para admitir datos y dispositivos en el mundo 5G. Arm Neoverse es una IP construida específicamente para este mercado que soporta muchas necesidades informáticas, desde una escala muy grande hasta un acceso extremo.

Noel Hurley dijo que la primera solución Arm Neoverse de la industria está diseñada para un nivel más alto de infraestructura de rendimiento, seguridad y escalabilidad. Las innovaciones desde el diseño de microarquitectura hasta el silicio, el software y los sistemas ayudan a diseñar soluciones de vanguardia que satisfacen las necesidades diversas y en constante cambio de todo el mundo de la informática.

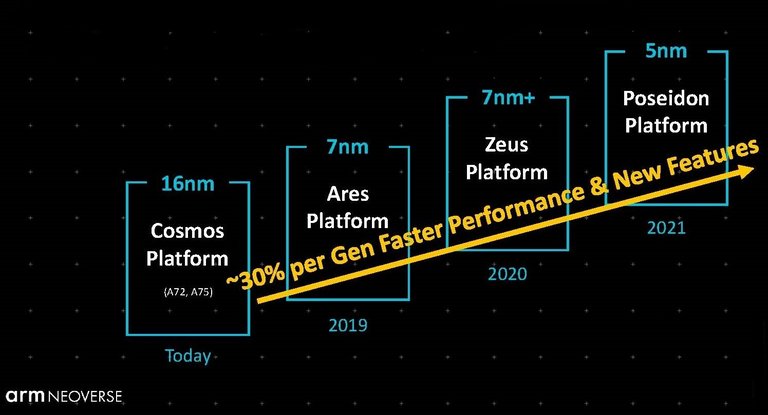

En el primer anuncio de Arm de la hoja de ruta IP del procesador Neoverse (Figura 1), se incluyen detalles preliminares sobre la plataforma optimizada para los nodos de proceso de vanguardia, y estas plataformas se lanzarán en un futuro próximo. La primera plataforma IP "Ares" basada en tecnología de 7 nm se lanzará a principios de 2019, y para 2021, cada generación de actualizaciones de la plataforma traerá hasta un 30% de mejora en el rendimiento. Diseñada para los requisitos únicos de rendimiento, eficiencia y escalabilidad, la Hoja de ruta de Neoverse IP se adapta a los patrones de datos cambiantes, los nuevos desafíos de la carga de trabajo y la infraestructura en evolución para admitir dispositivos inteligentes conectados a la red. Crecimiento continuo de la demanda. El lanzamiento de Neoverse destaca las inversiones continuas en curso de Arm y su ecosistema para ofrecer computación ubicua desde la nube hasta el borde, al tiempo que brinda el mejor rendimiento y la mejor eficiencia para la próxima generación de infraestructura distribuida de nube a borde.

Figura 1 En el procesador Neoverse, cada generación aportará un 30% de mejora del rendimiento y algunas características nuevas.

Arm Neoverse se centra en nuevos escenarios de infraestructura y aplicaciones, incluidos centros de datos en la nube a gran escala, soluciones de almacenamiento y redes 5G. Neoverse tiene tres pautas de diseño, una es una arquitectura y una arquitectura IP seguras y de alto rendimiento diseñadas para las cargas de trabajo en red y nativas de la nube; la otra es un conjunto de IP altamente escalable optimizado para los nodos de proceso líderes, incluido Ares (7 nm), Zeus (7 nm +) y Poseidon (5 nm) están diseñados para implementar sistemas en toda la infraestructura; en tercer lugar, crear un ecosistema sólido mediante el aprovechamiento de las inversiones en software unificado, herramientas y plataformas de silicio para desarrollar Una solución única y diversa para una variedad de escenarios de aplicación.

El diseño de arquitecturas de sistemas e IP para mercados clave como servidores, automóviles y redes es una prioridad para Arm durante el último año. Especialmente en el sector de infraestructura, Arm tiene una participación de mercado de casi el 30% como la arquitectura más implementada en la infraestructura global de Internet, no solo destacando el cambio en la arquitectura preferida, sino también destacando la popularidad de la tecnología Arm en todo el mercado de infraestructura.

Cortex-A76AE: el primer procesador de piloto automático integrado y funcionalmente seguro del mundo

Según Noel Hurley, el 90% de la inteligencia artificial del mundo opera en el núcleo del brazo. En los últimos 2 a 3 años, Arm ha realizado grandes inversiones en tecnología de inteligencia artificial, y pronto estarán disponibles algunos de los productos correspondientes. La tecnología de piloto automático es un área de aplicación muy desafiante para la inteligencia artificial.

De hecho, ya en 1996, Arm comenzó a ingresar al mercado automotriz, cuando Arm7 se usaba principalmente para soluciones de ABS. Desde entonces, Arm ha estado diseñando chips para aplicaciones automotrices. Actualmente, Arm es la única compañía en el mercado que puede proporcionar soluciones IP para todas las necesidades informáticas de los componentes. En la actualidad, los 15 fabricantes de chips automotrices más importantes del mundo están autorizados por Arm, y el chip basado en el brazo proporciona controladores para el 65% de las aplicaciones ADAS actuales y el 85% de las aplicaciones del sistema de entretenimiento para automóviles IVI. En la conducción autónoma más calurosa, el brazo se centra en dos áreas principales, el sistema de entretenimiento IVI para automóvil y el sistema avanzado de asistencia al conductor ADAS, que son los dos sistemas clave para vehículos autónomos.

La intención original de conducir de manera autónoma es eliminar lo más posible los accidentes de tráfico causados por errores humanos. Por lo tanto, al desarrollar SoC y sistemas de clase de piloto automático, la seguridad es tan importante como el rendimiento del sistema y la eficiencia energética. Arm IP tiene una participación de mercado de hasta el 65% en el chip de aplicación ADAS, y Arm siempre ha sido inseparable en seguridad. Dijo Noel hurley.

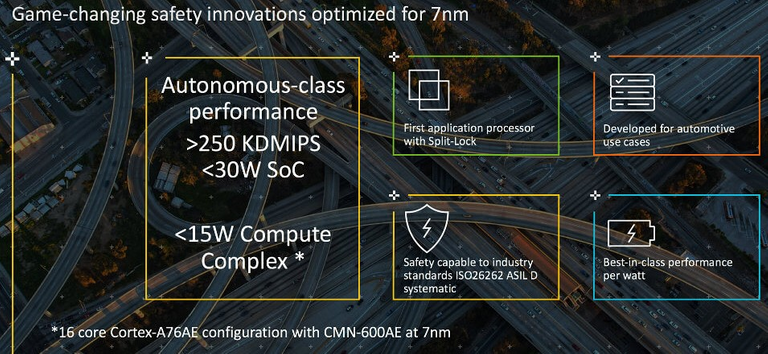

El piloto automático requiere un mayor nivel de potencia de procesamiento, donde la seguridad inherente será estándar. El Cortex-A76AE es el primer procesador de aplicaciones de alto rendimiento de la industria con bloqueo de división (Split-Lock), que combina el rendimiento de procesamiento y la alta integridad de seguridad del vehículo requerida para las aplicaciones de conducción autónoma. Aunque la función split-lock-lock no es ajena a la industria, Arm es el primero en introducirla en un procesador diseñado para aplicaciones automotrices de alto rendimiento, como la conducción autónoma, que se puede decir que es una innovación de seguridad disruptiva.

Figura 2 El primer procesador integrado de seguridad de piloto automático Cortex-A76AE del mundo.

La función split-lock-lock puede lograr el siguiente rendimiento: primero, tiene la flexibilidad que no se puede lograr en implementaciones anteriores de la CPU, y segundo, el clúster de CPU en el SoC se puede configurar en "modo básico" para un alto rendimiento, donde el clúster Se pueden utilizar dos (o cuatro) CPU independientes para diversas tareas y aplicaciones; tercero, si se configura en "modo de bloqueo", la CPU estará en estado de bloqueo, creando un par (o dos pares) en el clúster CPU con bloqueo de bloqueo para aplicaciones de mayor integridad de seguridad automotriz; en cuarto lugar, los clústeres de CPU pueden configurarse para operar en cualquier modo después de la producción de obleas.

De acuerdo con la hoja de ruta de IP automotriz de Arm, la Cortex-A76AE es la primera en una hoja de ruta de procesador "mejorada para automóviles" que ofrecerá la cartera más completa de productos de IP de seguridad funcional de la industria. La nueva hoja de ruta incluye las series "Helios-AE" y "Hercules-AE", todas optimizadas para el proceso de 7 nm.

La nueva API de PSA: la mejora de la protección de la seguridad de IoT de la cobertura del dispositivo a los datos

es un requisito previo clave para la adopción generalizada de cualquier tecnología emergente, al igual que el chip, el sistema y los datos de IoT. Para los dispositivos IoT, nunca se permite restablecer la seguridad porque la seguridad de los datos es equivalente a la confianza de las empresas y los consumidores en las aplicaciones innovadoras.

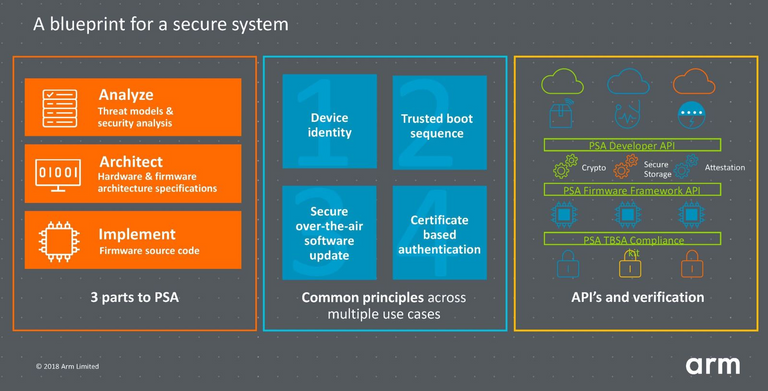

Hace un año, Arm presentó la Platform Security Architecture (PSA), un marco común que protege la seguridad de miles de millones de dispositivos conectados. Desde entonces, PSA ha seguido expandiéndose y ha ganado más apoyo de la industria, entregando entregables en todas las áreas de las tres etapas de desarrollo. Los archivos de modelos de amenazas, las especificaciones técnicas y el software de referencia se introdujeron a través del programa de Firmware de confianza de código abierto (TF-M). Después de un año de desarrollo, PSA se ha convertido en un elemento clave en la creación de dispositivos de redes confiables.

Hoy en día, el brazo de nuevo para PSA introdujo una nueva API y su conjunto de pruebas de compatibilidad que contiene desarrollador API PSA, PSA firmware API del marco, la SCT-M conjunto de pruebas de la arquitectura, y en cooperación con Cybereason para integrar el motor Cybereason AI para cazar Pelion cosas La plataforma protege el Internet de las cosas del dispositivo a los datos.

Figura 3 Arquitectura de seguridad de la plataforma PSA tiene como objetivo proporcionar un marco común para garantizar la seguridad de billones de dispositivos conectados

El nuevo conjunto de pruebas de compatibilidad de API y API de PSA admite tres áreas de diseño clave, que incluyen: API de desarrollador de PSA, disponible para proveedores de sistemas operativos en tiempo real (RTOS) y desarrolladores de software; API de marco de firmware de PSA para ayudar a los expertos en seguridad en el desarrollo Funciones de seguridad personalizadas; proporciona el conjunto de pruebas de arquitectura de sistema subyacente confiable (TBSA-M) para que los proveedores de chips prueben la compatibilidad del hardware del chip con las especificaciones PSA TBSA-M.

Para proteger la gran cantidad de superficies de ataque a las que se enfrentan miles de millones de dispositivos conectados, la complejidad involucrada es extremadamente alta, y la industria necesita trabajar en conjunto para crear un ecosistema que proteja por completo todo, desde los dispositivos hasta los datos.

El enfoque de Arm es fomentar toda la pila de soluciones, asegurando que los dispositivos de IoT sean tan seguros como la plataforma de IoT de Arm Pelion. La plataforma de IoT de Arm Pelion integra los principios de PSA y proporciona un mecanismo de seguridad de dispositivo a datos unificado que cubre el dispositivo de IoT y los datos. La solución proporciona seguridad de dispositivos PKI de vanguardia, comunicaciones seguras TLS de confianza, cifrado de datos y otros servicios, como actualizaciones de firmware de seguridad y control de acceso a dispositivos de campo.

De acuerdo con Noel Hurley, para implementar la estrategia "cualquier dispositivo, cualquier nube" de la plataforma Pelion IoT, Arm trabajó con Intel para eliminar las barreras a la expansión de IoT. Sobre la base de esta colaboración, la plataforma IoT de Arm's Pelion puede cargar y administrar plataformas de arquitectura Intel (x86) además de los dispositivos y puertas de enlace IoT basados en Arm. La administración de dispositivos Pelion de Arm combinada con el servicio Intel® a bordo de dispositivos de seguridad a bordo de dispositivos seguros (Intel SDO) permite a las organizaciones crear dispositivos sin tener que conocer las credenciales de carga inicial específicas del cliente final, incluso sin saber qué aplicación elegirá el usuario final. El marco permite un modelo de configuración de nube más flexible y proporciona una base compatible para los dispositivos Arm e Intel para la plataforma IoT de Arm Pelion para la carga inicial de cualquier nube de aplicaciones. Esta colaboración transformará a toda la industria de un estado de cadena de suministro aislado a un marco unificado para diseñar y abastecer dispositivos seguros y conectables.

El proyecto DesignStart se expande de nuevo, acelerando el diseño integrado basado en Linux

La misión del proyecto DesignStart es simplificar la forma en que se logra Arm Arm IP. En la última década, miles de chips se han transmitido con éxito. En el foro anual de tecnología de 2018, arm anunció que su proyecto DesignStart fue mejorado aún más. Basado en el Cortex-M0 y Cortex-M3, el Cortex-A5, el procesador de aplicaciones con el menor consumo de energía y la mayor eficiencia de área, se incluyó en el proyecto. El personal puede usar el procesador Arm que soporta Linux en diseños avanzados.

Hasta la fecha, el Cortex-A5 ha proporcionado capacidades de procesamiento de alto rendimiento y con muchas funciones para más de 2 mil millones de dispositivos, y ha sido seleccionado por los principales proveedores de la nube como un punto de entrada para el procesamiento de IoT de extremo a extremo. La adición del Cortex-A5 lleva el proyecto Arm DesignStart a un nivel completamente nuevo.

Antes de esto, Arm acaba de anunciar la introducción de una tarifa de licencia cero y un procesador Cortex-M sin royalties para los FPGA de Xilinx en el proyecto DesignStart. Llevar los beneficios del procesador Arm Cortex-M al desarrollo del proyecto FPGA a través del proyecto DesignStart, proporcionando una arquitectura de procesador escalable y estandarizada para la cartera de Xilinx. Al mismo tiempo, a través de las herramientas de Xilinx y las soluciones integrales de desarrollo de software, los desarrolladores pueden adquirir y usar de manera rápida y rentable las IP de los procesadores probados en la industria para facilitar la integración del diseño con las herramientas de Xilinx, acelerando así el éxito de los proyectos FPGA. .

Espero haya sido de interés, Que las bendiciones del Señor este con ustedes y en su hogar, les deseo éxito y gracias por apoyar

Imagenes y Fuente: China Business electrónico - Globb Security - Neoverse N1 – Arm